2. Alat dan bahan[Kembali]

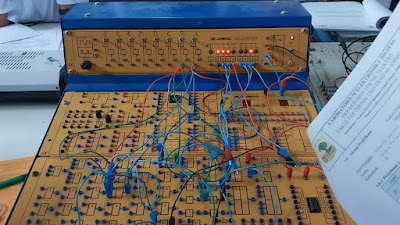

1. Panel DL 2203C

2. Panel DL 2203D

3. Panel DL 2203S

4. Kabel Jumper

3. Rangkaian Simulasi[Kembali]

Gambar rangkaian pada saat percobaan praktikum

Gambar Rangkaian Pada Proteus

4. Prinsip Kerja[Kembali]

Dalam sistem dengan logic state sebagai input, logic probe sebagai output, dan menggunakan clock untuk melihat output gelombang kotak, terdapat berbagai jenis gerbang logika yang memiliki prinsip kerja yang berbeda. Gerbang NOT melakukan inversi terhadap inputnya, di mana jika input berlogika 0, output akan berlogika 1, dan sebaliknya. Gerbang AND menghasilkan output berlogika 0 jika setidaknya satu inputnya berlogika 0, dan output baru berlogika 1 jika kedua inputnya berlogika 1. Gerbang OR menghasilkan output berlogika 1 jika setidaknya satu inputnya berlogika 1, dan output berlogika 0 hanya jika kedua inputnya berlogika 0. Gerbang NOR menghasilkan output berlogika 1 jika setidaknya satu inputnya berlogika 0, dan output berlogika 0 hanya jika semua inputnya berlogika 1. Gerbang NAND menghasilkan output berlogika 1 jika setidaknya satu inputnya berlogika 0, dan output baru berlogika 0 jika kedua inputnya berlogika 1. Gerbang XOR menghasilkan output berlogika 0 jika kedua inputnya memiliki logika yang sama (keduanya 0 atau keduanya 1), dan output berlogika 1 hanya jika salah satu inputnya berbeda dengan input yang lain. Gerbang XNOR menghasilkan output berlogika 1 jika kedua inputnya memiliki logika yang sama (keduanya 0 atau keduanya 1), dan output berlogika 0 hanya jika salah satu inputnya berbeda dengan input yang lain.

Jika B1 diganti dengan clock, prinsip kerja gerbang logika tersebut akan menghasilkan pola output yang berbeda. Pada gerbang NOT, output akan menjadi gelombang dengan pola 1010. Pada gerbang AND, output akan berlogika 0 ketika kondisi input adalah 0, dan output akan berlogika 0101 ketika kondisi input adalah 1. Pada gerbang OR, output akan berlogika 0101 ketika kondisi input adalah 0, dan output akan berlogika 1 ketika kondisi input adalah 1. Pada gerbang XOR, output akan berlogika 0101 ketika kondisi input adalah 0, dan output akan berlogika 1010 ketika kondisi input adalah 1. Pada gerbang NAND, output akan berlogika 1 ketika kondisi input adalah 0, dan output akan berlogika 1010 ketika kondisi input adalah 1. Pada gerbang NOR, output akan berlogika 1010 ketika kondisi input adalah 0, dan output akan berlogika 0 ketika kondisi input adalah 1. Pada gerbang XNOR, output akan berlogika 1010 ketika kondisi input adalah 0, dan output akan berlogika 0101 ketika kondisi input adalah 1. Dengan penggunaan clock, output dari gerbang logika ini dapat disinkronkan dengan perubahan fase naik clock yang ditentukan.

Percobaan 1:

1. Analisa Pengaruh clock terhadap masing-masing output gerbang logika

Saat clock berada pada fase naik (rising edge), pengaruh pada masing-masing output gerbang berlogika adalah sebagai berikut:

Gerbang Logika AND: output akan menjadi berlogika tinggi (1) hanya jika semua inputnya juga berlogika tinggi (1). Jika ada setidaknya satu input yang berlogika rendah (0), output akan tetap berlogika rendah (0). Dapat dilihat pada jurnal percobaan saat inputnya 1 dan clock maka outputnya seperti clock. Jika inputnya 0 dan clock maka outputnya berlogika rendah (0).

Gerbang Logika OR: output akan menjadi berlogika tinggi (1) jika setidaknya satu inputnya berlogika tinggi (1). Jika semua inputnya berlogika rendah (0), output akan tetap berlogika rendah (0). Dapat dilihat pada jurnal percobaan Saat inputnya 1 dan clock maka outputnya Selalu 1. Jika inputnya 0 dan clock maka outputnya sama seperti clock (0).

Gerbang Logika NOT: output akan menjadi kebalikan (inversi) dari inputnya. Jika inputnya berlogika tinggi (1), output akan berlogika rendah (0), dan sebaliknya. Dapat dilihat pada jurnal percobaan output yang dihasilkan adalah kebalikan (inverse) dari clock.

Gerbang Logika XOR: output akan menjadi berlogika tinggi (1) jika jumlah input yang berlogika tinggi (1) adalah ganjil. Jika jumlah input yang berlogika tinggi (1) adalah genap, output akan berlogika rendah (0). Dapat dilihat pada jurnal percobaan Saat inputnya 1 dan clock maka outputnya inverse dari clock. Jika inputnya 0 dan clock maka outputnya sama seperti clock.

Gerbang Logika NAND: output gerbang NAND akan menjadi berlogika rendah (0) jika semua inputnya berlogika tinggi (1). Jika setidaknya satu input berada pada berlogika rendah (0), maka output akan menjadi berlogika tinggi(1). Dapat dilihat pada jurnal percobaan saat inputnya 1 dan clock maka outputnya inverse (kebalikan) dari clock. Jika inputnya 0 dan clock maka outputnya selalu berlogika tinggi (1).

Gerbang Logika NOR: output gerbang NOR akan menjadi tinggi (1) jika semua inputnya rendah (0). Jika setidaknya satu input berada pada nilai tinggi (1), maka output akan menjadi rendah (0). Dapat dilihat pada jurnal percobaan saat inputnya 1 dan clock maka outputnya selalu berlogika rendah(0). Jika inputnya 0 dan clock maka outputnya inverse dari clock.

Gerbang Logika XNOR: output gerbang XNOR akan menjadi tinggi (1) jika jumlah input yang bernilai logika tinggi (1) adalah genap. Jika jumlah input yang bernilai logika tinggi (1) adalah ganjil, maka output akan menjadi rendah (0). Dapat dilihat pada jurnal percobaan saat inputnya 1 dan clock maka outputnya seperti clock. Jika inputnya 0 dan clock maka outputnya inverse dari clock.

2. Analisa output gerbang logika jika kedua input dihubungkan dengan clock yang sama

(analisa menggunakan semua jenis gerbang logika) gambarkan sinyal outputnya!

Dalam gerbang logika, pengaruh clock pada setiap jenis gerbang adalah sebagai berikut:

1. Gerbang Logika AND:

- Saat fase naik clock, output gerbang AND akan berlogika tinggi (1) hanya jika kedua inputnya berlogika tinggi (1). Jika minimal satu input atau kedua input berlogika rendah (0), output akan tetap berlogika rendah (0). Perubahan output terjadi hanya pada fase naik clock.

2. Gerbang Logika OR:

- Saat fase naik clock, output gerbang OR akan berlogika tinggi (1) jika minimal satu dari kedua inputnya berlogika tinggi (1). Jika kedua input berlogika rendah (0), output akan tetap berlogika rendah (0). Perubahan output terjadi hanya pada fase naik clock.

3. Gerbang Logika NOT:

- Gerbang NOT memiliki satu input. Pengaruh clock pada gerbang NOT tidak berlaku secara langsung karena tidak ada perubahan input yang terjadi pada fase naik clock. Output gerbang NOT akan menghasilkan kebalikan (inversi) dari nilai inputnya.

4. Gerbang Logika XOR:

- Saat fase naik clock, output gerbang XOR akan berlogika tinggi (1) jika jumlah input yang berlogika tinggi (1) adalah ganjil. Jika jumlah input yang berlogika tinggi (1) adalah genap, output akan berlogika rendah (0). Perubahan output terjadi hanya pada fase naik clock.

5. Gerbang Logika NAND:

- Saat fase naik clock, output gerbang NAND akan berlogika rendah (0) jika kedua inputnya berlogika tinggi (1). Jika minimal satu input atau kedua input berlogika rendah (0), output akan tetap berlogika tinggi (1). Perubahan output terjadi hanya pada fase naik clock.

6. Gerbang Logika NOR:

- Saat fase naik clock, output gerbang NOR akan berlogika rendah (0) jika minimal satu dari kedua inputnya berlogika tinggi (1). Jika kedua input berlogika rendah (0), output akan tetap berlogika tinggi (1). Perubahan output terjadi hanya pada fase naik clock.

7. Gerbang Logika XNOR:

- Saat fase naik clock, output gerbang XNOR akan berlogika tinggi (1) jika jumlah input yang berlogika tinggi (1) adalah genap. Jika jumlah input yang berlogika tinggi (1) adalah ganjil, output akan berlogika rendah (0). Perubahan output terjadi hanya pada fase naik clock.

5. Link Download

[Kembali]

➤Download HTMLklik disini

➤Download Simulasi Rangkaianklik disini

➤Download Video Praktikumklik disini

_1.jpg)

Tidak ada komentar:

Posting Komentar